Running CoreMark on SonicBOOM Simulator

Luffcaでは、アウトオブオーダ実行スーパースカラのRISC-V CPUであるSonicBOOMのSFB(Short-Forwards Branch)最適化を有効化したシミュレータを作成し、CoreMarkを実行しました。

結果は、ee_u32をunsigned intからsigned intに変更した場合と変更しない場合において、それぞれCoreMark/MHz 6.89と6.45でした。

これらの結果は、SonicBOOMが6.2 CoreMark/MHzの公称値を達成できることを示しています。

BOOM

Berkeley Out-of-Order Machine(BOOM)は、前回の記事で紹介したChipyardに含まれるRTLジェネレータの一つで、アウトオブオーダ実行スーパースカラのRISC-V CPUを生成することができます。

現在は、SonicBOOMとも呼ばれるBOOMv3(BOOM version3)です。

SonicBOOMのCoreMark/MHzの公称値は、6.2です。

SFB optimization

SFB(Short-Forwards Branch)最適化は、SonicBOOM: The 3rd Generation Berkeley Out-of-Order Machineにおいて、以下のように記述されています。

As an example, SonicBOOM achieves 6.15 CoreMark/MHz with the SFB optimization enabled, compared to 4.9 CoreMark/MHz without.

ところが、このSFB最適化が、デフォルトでは有効になっていません。

BOOM Simulator

作成したBOOMシミュレータは、Verilatorを使用する以下の2つのシミュレータです。

simulator-chipyard-MegaBoomConfig: デフォルト(SFB最適化なし)simulator-chipyard-MegaBoomConfig-SFB: SFB最適化あり

BOOMの構成にはいくつかの種類がありますが、4-wide BOOM構成のMegaBoomシミュレータを作成しました。

CoreMark

CoreMarkは、Chipyardに含まれているriscv-coremarkをベースにしています。

下の表に示すように、4種類のCoreMarkをビルドしました。それらは、CFLAGSが-O2と-O3の2種類、ee_u32がデフォルトのunsigned intとsigned intの2種類の組み合わせです。

| ee_u32 | |||

|---|---|---|---|

| unsigned int | signed int | ||

| CFLAGS | -O2 | coremark.o2-u32 | coremark.o2-s32 |

| -O3 | coremark.o3-u32 | coremark.o3-s32 | |

なお、CoreMarkのITERATIONSは10、CoreMarkのビルドにはGCC 11.1.0を使用しています。

Running CoreMark on BOOM Simulator

Default ee_u32

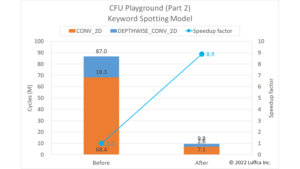

下の表は、ee_u32にunsigned intを使用するデフォルトのCoreMarkを用いた結果を示しています。

| CoreMark/MHz | SFB Optimization | ||

|---|---|---|---|

| Disabled | Enabled | ||

| CFLAGS | -O2 | 5.49 | 6.45 |

| -O3 | 5.94 | 5.97 | |

SFB最適化ありのBOOMシミュレータは、-O2でビルドしたCoreMarkの実行時に、公称値の6.2 CoreMark/MHzを上回る6.45 CoreMark/MHzを達成しています。

これに対し、SFB最適化なしのBOOMシミュレータは、-O3でビルドしたCoreMarkの実行時に、5.94 CoreMark/MHzです。

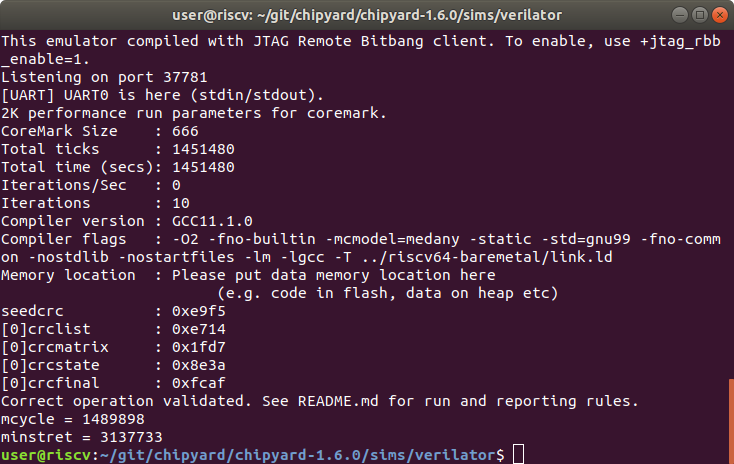

以下は、-O2でビルドしたCoreMarkを実行した時のSFB最適化ありBOOMシミュレータの出力です。

$ ./simulator-chipyard-MegaBoomConfig-SFB coremark.o2-u32 This emulator compiled with JTAG Remote Bitbang client. To enable, use +jtag_rbb_enable=1. Listening on port 37541 [UART] UART0 is here (stdin/stdout). 2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 1551464 Total time (secs): 1551464 Iterations/Sec : 0 Iterations : 10 Compiler version : GCC11.1.0 Compiler flags : -O2 -fno-builtin -mcmodel=medany -static -std=gnu99 -fno-common -nostdlib -nostartfiles -lm -lgcc -T ../riscv64-baremetal/link.ld Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0xfcaf Correct operation validated. See README.md for run and reporting rules. mcycle = 1589202 minstret = 3569373

CoreMarkの10回の繰り返しがTotal ticks欄の1,551,464サイクルなので、上の表のように、CoreMark/MHzは6.45になります。

Modified ee_u32

下の表は、ee_u32にsigned intを使用するCoreMarkを用いた結果を示しています。

| CoreMark/MHz | SFB Optimization | ||

|---|---|---|---|

| Disabled | Enabled | ||

| CFLAGS | -O2 | 5.84 | 6.89 |

| -O3 | 6.27 | 6.31 | |

SFB最適化ありのBOOMシミュレータのCoreMark/MHzは、-O2でビルドしたCoreMarkの実行時に、公称値の6.2を上回る6.89です。

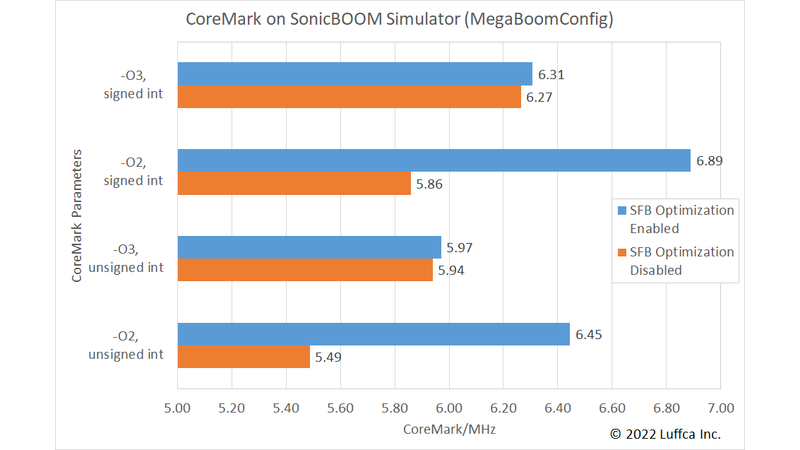

下の図は、-O2でビルドしたCoreMarkを実行した時のSFB最適化ありのBOOMシミュレータの出力です。

CoreMarkの10回の繰り返しがTotal ticks欄の1,451,480サイクルなので、上の表のように、CoreMark/MHzは6.89になります。

まとめ

Luffcaでは、SFB(Short-Forwards Branch)最適化を有効化したSonicBOOMのシミュレータを作成し、CoreMarkを実行しました。

結果は、ee_u32をunsigned intからsigned intに変更した場合と変更しない場合において、それぞれCoreMark/MHz 6.89と6.45でした。

これらの結果は、SonicBOOMが6.2 CoreMark/MHzの公称値を達成できることを示しています。