TensorFlow Lite for Microcontrollers on RISC-V Out-of-Order Core

Luffcaでは、RISC-V Out-of-Order CoreのNaxRiscvを実装したFPGAボード上で、GoogleのTensorFlow Lite for Microcontrollersを実行することに成功しました。

NaxRiscvの関連記事は、こちら。

TensorFlow Lite for Microcontrollers

TensorFlow Lite for Microcontrollers(以下、TFLite Micro)リポジトリには、以下のように記述されています。

TensorFlow Lite for Microcontrollers is a port of TensorFlow Lite designed to run machine learning models on DSPs, microcontrollers and other devices with limited memory.

簡単に言うと、TFLite Microは、OSなしで動作するTensorFlow Liteのベアメタルバージョンです。

NaxRiscv

NaxRiscvは、アウトオブオーダ実行スーパースカラのRISC-V Coreであり、SoC builderのLiteXに統合されています。NaxRiscvの概要は、関連記事のBenchmarks on RISC-V Out-of-Order Simulatorをご覧ください。

今回は、Running 32-bit Linux on FPGAs with RISC-V Out-of-Order Coreの記事で紹介したDigilent社のNexys Video用の32-bit NaxRiscvのゲートウェアを使用しました。

TFLite Micro on FPGA with NaxRiscv

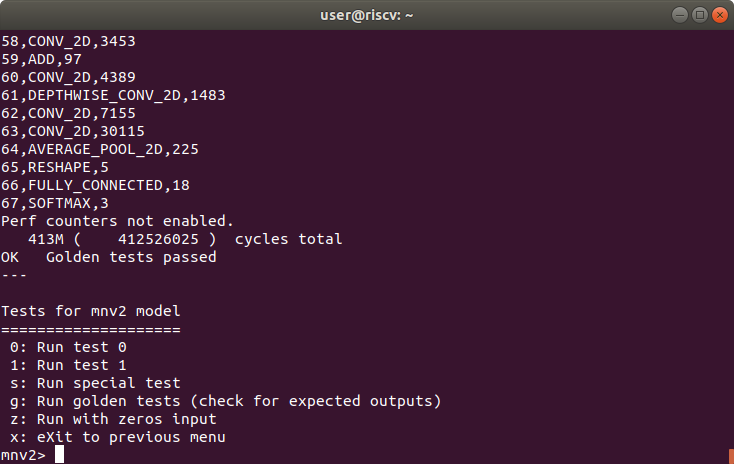

Result of golden tests for MobileNetV2 model

32-bit NaxRiscvのゲートウェアをFPGAボードのNexys Videoにロードし、TFLite MicroのKeyword Spotting、Person Detection及びMobileNetV2モデルを実行しました。

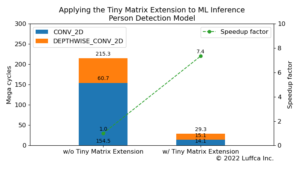

アイキャッチ画像と下の表は、インオーダ実行スカラのRISC-V CoreであるVexRiscvと比較した結果を示しています。

| ML models | Mega cycles | Speedup factor |

|

|---|---|---|---|

| VexRiscv | NaxRiscv | ||

| Keyword Spotting | 87 | 33 | 2.64 |

| Person Detection | 215 | 79 | 2.72 |

| MobileNetV2 | 1079 | 413 | 2.61 |

VexRiscvと比較したスピードアップは、およそ2.6倍です。

まとめ

Luffcaでは、アウトオブオーダ実行スーパースカラのRISC-V CoreであるNaxRiscvを実装したFPGAボード上で、GoogleのTFLite Microを実行することに成功しました。インオーダ実行スカラのRISC-V CoreであるVexRiscvと比較すると、スピードアップはおよそ2.6倍です。