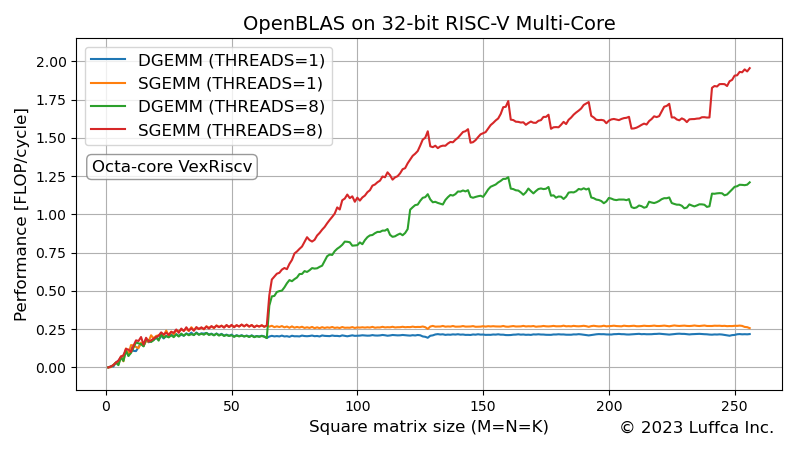

OpenBLAS on 32-bit RISC-V Multi-Core

Luffcaでは、OpenBLASを32-bit RISC-Vに対応させ、FPGAボードに8コアの32-bit RISC-V SoCを実装して、GEMM(GEneral Matrix-to-matrix Multiply)の性能を評価しました。

OpenBLAS

OpenBLASのREADME.mdのIntroductionに以下の記載があるように、OpenBLASはオープンソースの最適化BLAS実装です。

OpenBLAS is an optimized BLAS (Basic Linear Algebra Subprograms) library based on GotoBLAS2 1.13 BSD version.

RISC-Vの対応状況として、最新リリースv0.3.21のTargetList.txtには、64-bit RISC-V用のRISCV64_GENERICとRISC-V Vector(0.7.1)をサポートするXuanTie C910用のC910Vがあります。

OpenBLAS for RV32GC

VexRiscvは、RISC-Vの単精度浮動小数点拡張Fに対応しており、32-bit RISC-Vには珍しく倍精度浮動小数点拡張Dにも対応しています。ここでは、RV32IMAFDC(RV32GC)をサポートするVexRiscv用にOpenBLASをビルドしました。

また、OpenMPを有効にするため、USE_OPENMP=1オプションを追加してビルドしています。

GEMM on Octa-Core VexRiscv

8コアのVexRiscv SoCを実装したFPGAボードのNexys Videoと、Buildrootを用いて作成したLinux環境を組み合わせて、DGEMM(倍精度GEMM)とSGEMM(単精度GEMM)の性能を評価しました。このSoCは、OpenMP on FPGA with RISC-V Multi-Core Processorの記事で紹介しているものです。

以下は、スレッド数8のSGEMMを実行したときのコンソール出力を表しています。環境変数OPENBLAS_LOOPSに10を設定することにより、10回の平均性能を算出しています。

root@buildroot:/home# export OPENBLAS_LOOPS=10

root@buildroot:/home# export OMP_NUM_THREADS=8

root@buildroot:/home# ./sgemm.goto 1 256

From : 1 To : 256 Step=1 : Transa=N : Transb=N

SIZE Flops Time

M= 1, N= 1, K= 1 : 0.04 MFlops 0.000468 sec

M= 2, N= 2, K= 2 : 0.60 MFlops 0.000268 sec

M= 3, N= 3, K= 3 : 1.55 MFlops 0.000349 sec

...

M= 254, N= 254, K= 254 : 194.70 MFlops 1.683302 sec

M= 255, N= 255, K= 255 : 193.38 MFlops 1.714861 sec

M= 256, N= 256, K= 256 : 195.52 MFlops 1.716203 sec

アイキャッチ画像は、DGEMMとSGEMMの性能(FLOP/cycle)を表しています。VexRiscvの動作周波数は100MHzなので、1FLOP/cycleが、100MFLOPSに対応します。

まとめ

Luffcaでは、OpenBLASを32-bit RISC-Vに対応させ、FPGAボードのNexys Videoに8コアのVexRiscv SoCを実装して、GEMMの性能を評価しました。