Testing LiteX/VexRiscv on Sipeed Tang Primer

SoCビルダーのLiteXに、Sipeed社のFPGAボードであるTang PrimerとAnlogic社のFPGAのイニシャル・サポートが追加されたので、SoCを作成してみました。

これらのSoCは、https://github.com/litex-hub/litex-boards等をベースにしています。

関連記事は、こちら。

- Porting PicoSoC with PicoRV32 to Sipeed Tang Primer

- Testing LiteX/VexRiscv on Sipeed Tang Primer(本記事)

- Running Dual-Core RISC-V Linux on Cheap FPGA Board

Sipeed Tang Primer

Sipeed社のTang Primerは、Anlogic社のFPGA EG4S20BG256を用いた、ローコストFPGAボードです。

LiteX Initial Support for Tang Primer

以下が追加されています。

litex-boards: Sipeed社のTang Primerのイニシャル・サポートlitex: Anlogic社のFPGAのイニシャル・サポート

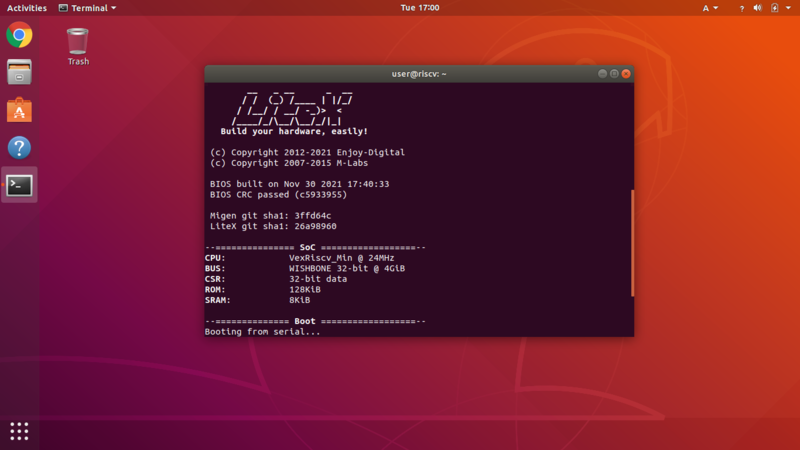

今回のサポートでは、CPUタイプが32-bit RISC-VのVexRiscvの場合、CPUバリアントはminimal(VexRiscv_Min)に限定されています。

また、SDRAMとSDカードは、サポートされていません。

アイキャッチ画像は、このSoCのUART出力です。

Testing LiteX/VexRiscv on Tang Primer

CPUバリアントの限定を削除して、CPUバリアントをstandardに変更したSoCは、UART出力がありません。

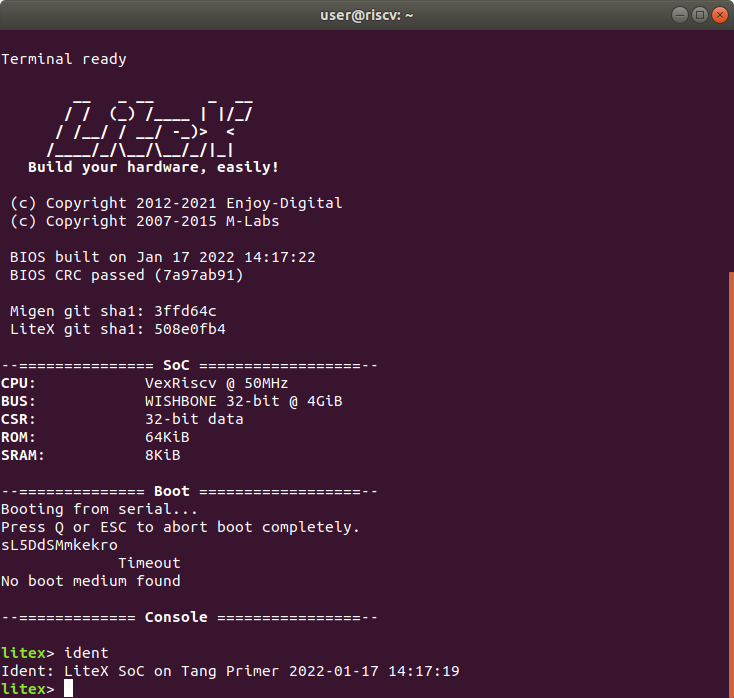

キャッシュサイズを0に変更したVexRiscvのstandardバリアント(VexRiscv)を用いたSoCは、UART出力がありました。

更に、PLLを追加して、system clock frequencyを24MHzから50MHzに変更したSoCを作成しました。

下の画像は、このSoCのUART出力です。

まとめ

LiteXにSipeed Tang PrimerとAnlogic社のFPGAのイニシャル・サポートが追加されたので、SoCを作成してみました。

キャッシュサイズを0に変更したVexRiscvのstandardバリアントを用いたSoCは、UARTから出力がありました。