Testing LiteX/VexRiscv on Sipeed Tang Primer

With the addition of initial support for Sipeed Tang Primer and Anlogic FPGA to LiteX, an SoC builder, we tried to create SoCs.

These SoCs are based on https://github.com/litex-hub/litex-boards etc.

Click here for related articles.

- Porting PicoSoC with PicoRV32 to Sipeed Tang Primer

- Testing LiteX/VexRiscv on Sipeed Tang Primer (this article)

- Running Dual-Core RISC-V Linux on Cheap FPGA Board

Sipeed Tang Primer

Tang Primer is a low-cost FPGA board from Sipeed.

The board features an Anlogic EG4S20BG256 FPGA.

LiteX Initial Support for Tang Primer

litex-boards: Add initial support for Sipeed Tang Primerlitex: Add initial support for Anlogic devices

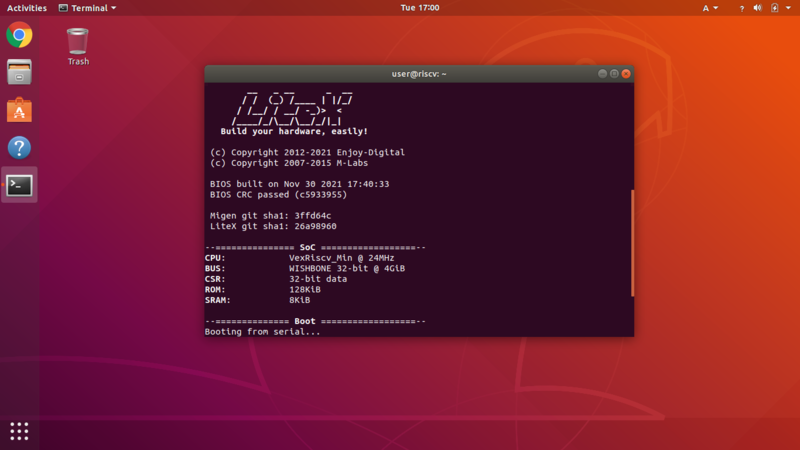

With this support, if the CPU type is 32-bit RISC-V VexRiscv, the CPU variant is limited to minimal (VexRiscv_Min).

Also, SDRAM and SD cards are not supported.

The featured image shows the UART output of this SoC.

Testing LiteX/VexRiscv on Tang Primer

The SoC with the CPU variant limitation removed and the CPU variant changed to standard has no UART output.

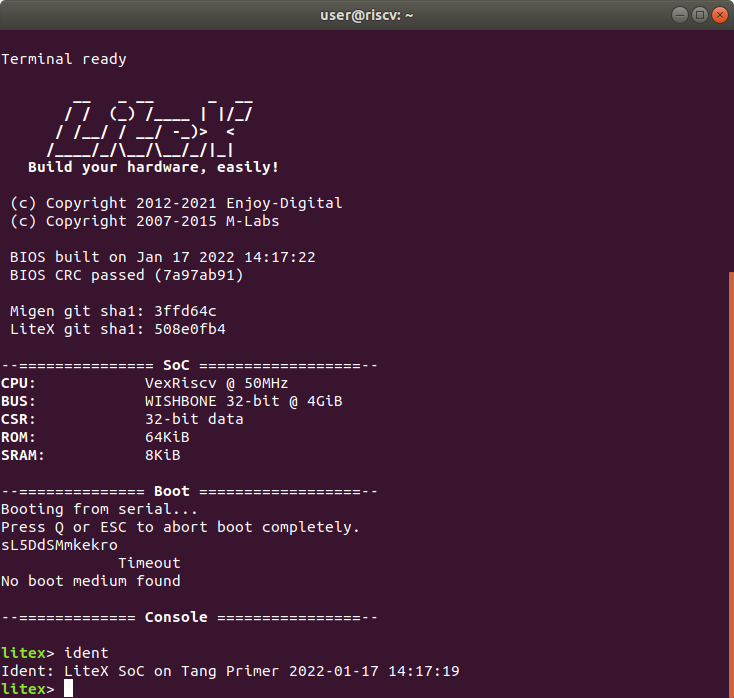

The SoC using the standard variant of VexRiscv (VexRiscv) with the cache size changed to 0 had output from the UART.

In addition, we added a PLL to create an SoC with the system clock frequency changed from 24 MHz to 50 MHz.

The image below shows the UART output of this SoC.

Summary

With the addition of initial support for Sipeed Tang Primer and Anlogic FPGA to LiteX, we tried to create SoCs.

The SoC using the standard variant of VexRiscv with the cache size changed to 0 had UART output.