Vortex: OpenCL Compatible RISC-V Based GPGPU (Part 1)

この記事では、RISC-VベースのオープンソースGPGPUであるVortexの全体像と、Vortexシミュレータを用いてOpenCLプログラムを実行する方法を紹介します。

Vortex

Vortexは、RISC-V ISAにGPGPUのためのカスタム命令を追加したSIMT(single instruction, multiple threads)実行モデルのGPGPUプロセッサです。VortexリポジトリのREADME.mdには、Specificationsとして以下の記載があります。

Specifications

- Support RISC-V RV32IMF ISA

- Performance:

- 1024 total threads running at 250 MHz

- 128 Gflops of compute bandwidth

- 16 GB/s of memory bandwidth

- Scalability: up to 64 cores with optional L2 and L3 caches

- Software: OpenCL 1.2 Support

- Supported FPGAs:

- Intel Arria 10

- Intel Stratix 10

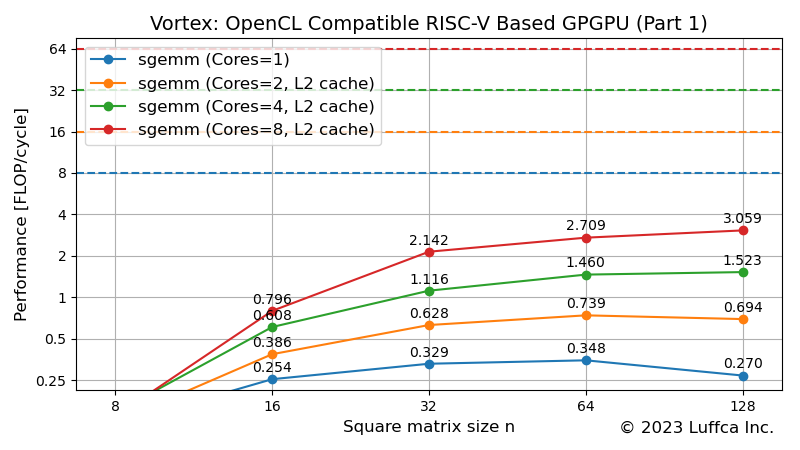

Microarchitecture

Vortexリポジトリのdocs/microarchitecture.mdには、マイクロアーキテクチャとして下の図が紹介されています。下図の上段が、Vortexコアを表しています。各ステージにスレッドとワープのための機能が追加されていることが分かります。ExecuteステージのGPGPUユニットは、GPGPUのためのカスタム命令を処理します。

VortexコアのグループがVortexクラスタであり、VortexクラスタのグループがVortexプロセッサです。VortexコアとVortexクラスタは、それぞれL2とL3キャッシュを共有できます。

Vortex Simulation Methods

Vortexのシミュレーション方法としては、Verilatorを用いるRTLシミュレーションのvlsimとrtlsim、Cycle-Approximateシミュレーションのsimx、FPGAボードを用いるFPGAシミュレーションのfpgaがあります。

Vortexのシミュレーション実行は、ciディレクトリのシェルスクリプトblackbox.shに統合されています。上記4つのシミュレーション方法は、コマンドライン引数を用いて切替可能です。

同様に、blackbox.shのコマンドライン引数を用いて、Vortexプロセッサの構成として、クラスタ数、コア数、ワープ数、スレッド数、L2及びL3キャッシュの有効/無効を変更できます。デフォルトの構成は、クラスタ数:1、コア数:4、ワープ数:4、スレッド数:4、L2とL3キャッシュ:無効です。

Running sgemm on Vortex RTL Simulator

Vortexプロセッサの構成を変化させて、tests/openclディレクトリ内のOpenCLプログラムsgemmを実行しました。このsgemmは、単精度GEMM(GEneral Matrix-to-matrix Multiply)の簡略版です。

$ cd $VORTEX $ ./ci/blackbox.sh --driver=rtlsim --cores=[1|2|4|8] [--l2cache] --app=sgemm --args="-n[4|8|16|32|64|128]"

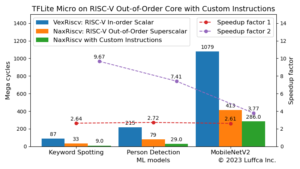

アイキャッチ画像は、シミュレーション結果から算出したPerformance (FLOP/cycle)を表しています。

まとめ

この記事では、RISC-VベースのオープンソースGPGPUであるVortexの全体像と、Vortexシミュレータを用いてtests/openclディレクトリ内のOpenCLプログラムsgemmを実行する方法を紹介しました。