RISC-V Bit-Manipulation ISA-extensions

In this article, we introduce the RISC-V Bit-Manipulation extension based on “RISC-V Bit-Manipulation ISA-extensions“, which was ratified in November 2021.

If you search the Internet for the RISC-V Bit-Manipulation (bitmanip) extension, you will find many articles with old content. If the article contains the following description, the content may be outdated.

- Referenced spec is not v1.0.0

- Describes extensions other than Zba, Zbb, Zbc and Zbs

- Described as B extension (or RVB)

BitManip Zba, Zbb, Zbc and Zbs extensions

In v1.0.0 of the ratified bitmanip specification, the bitmanip extension collection consists of four Zb* extensions:

- Zba: Address generation instructions

- Zbb: Basic bit-manipulation

- Zbc: Carry-less multiplication

- Zbs: Single-bit instructions

The bitmanip specification v0.93 describes 10 Zb* extensions, so v1.0.0 keeps things simple.

Relationship between misa.B and Zb* extensions

In the latest “The RISC-V Instruction Set Manual Volume II: Privileged Architecture”, misa.B is “Reserved” and is not related to bitmanip Zb* extensions.

Specifically, the January 26, 2022 commit c1c77c4, misa.B is changed from “Tentatively reserved for Bit-Manipulation extension” to “Reserved”.

Also, v0.93 of the bitmanip specification states that 8 types of Zb* extensions correspond to the B extension, but v1.0.0 does not state that they correspond to the B extension.

QEMU

The QEMU ChangeLog/6.2 has the following description of the bitmanip extension for RISC-V.

RISC-V

- Add Zb[abcs] instruction support

- Remove RVB support

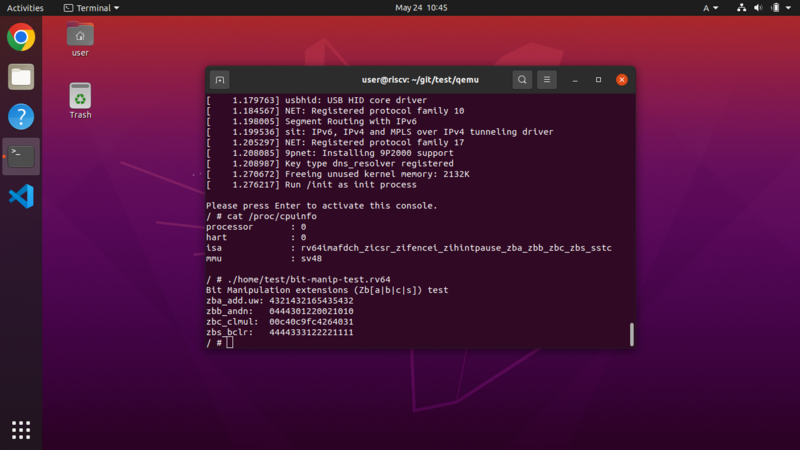

The featured image and console output below show the result of running cat /proc/cpuinfo in QEMU 7.2 with four Zb* extensions enabled.

/ # cat /proc/cpuinfo processor : 0 hart : 0 isa : rv64imafdch_zicsr_zifencei_zihintpause_zba_zbb_zbc_zbs_sstc mmu : sv48

Looking at the isa output, we can see zba_zbb_zbc_zbs corresponding to the four Zb* extensions, but there is no b corresponding to misa.B.

Rocket Chip

Also, misa.B is not used in Rocket Chip, a RISC-V implementation supporting the ratified Zb* extensions since commit 4ecc497.

Summary

In this article, we introduced the RISC-V bitmanip extension. If you search the Internet for bitmanip extension, you will find many articles with old content, so we recommend checking the ratified specification.