Running RISC-V Debian on FPGA boards using Vivado

We have succeeded in configuring SoCs with 64-bit RISC-V Rocket Chip using Vivado, and running RISC-V Debian on two FPGA boards, the Qmtech Wukong board and the Digilent Nexys Video.

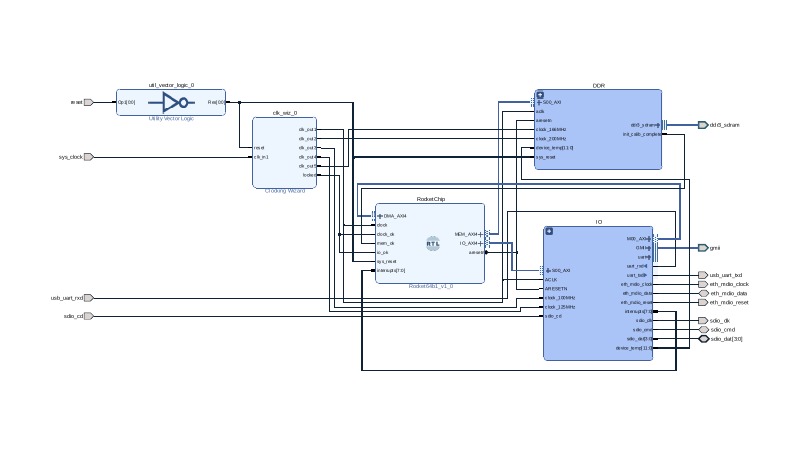

These SoCs are based on https://github.com/eugene-tarassov/vivado-risc-v.

Debian

Debian is one of the Linux distributions and supports RISC-V.

The Debian port uses RV64GC as the hardware baseline and the lp64d ABI (the default ABI for RV64G systems).

See RISC-V – Debian Wiki for more information.

vivado-risc-v

The prebuilt bitstream are available in the leases area for following FPGA boards.

- Xilinx VC707

- Xilinx KC705

- Digilent Genesys 2

- Digilent Nexys Video

- Digilent Nexys A7 100T

We created an SoC for Qmtech Wukong board (especially DRAM and Ethernet) based on this repository.

The Wukong board with XC7A100T only supports single bigcore called rocket64b1, but the Nexys Video with XC7A200T also supports dual bigcore rocket64b2.

This time we wrote the prepared SD card image to the SD card and ran Debian.

The boot sequence is as follows.

OpenSBI -> U-Boot -> Linux -> Debian rootfs

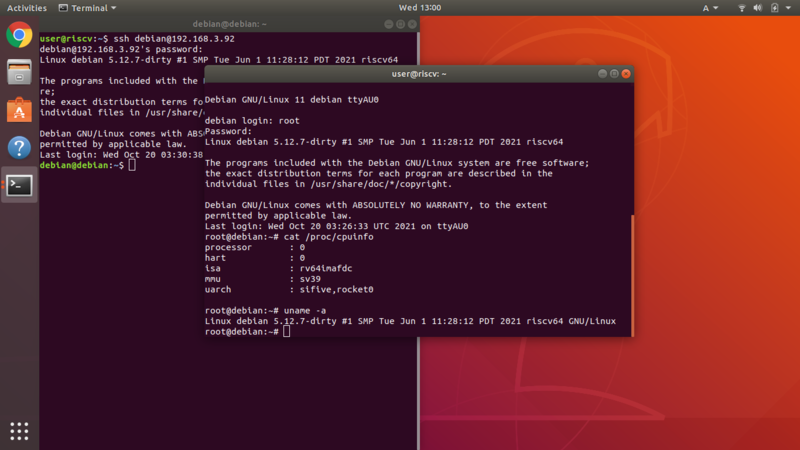

The screenshot shows the central terminal connected by UART and the terminal on the left connected by ssh via Ethernet.

Summary

We have succeeded in configuring SoCs with 64-bit RISC-V Rocket Chip using Vivado, and running RISC-V Debian on the Qmtech Wukong board and the Digilent Nexys Video.